- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Final polishing of the silicon wafer surface

2024-10-25

To achieve the high-quality requirements of IC chip circuit processes with line widths smaller than 0.13μm to 28nm for 300mm diameter silicon polishing wafers, it is essential to minimize contamination from impurities, such as metal ions, on the wafer's surface. Additionally, the silicon wafer must exhibit extremely high surface nanomorphology characteristics. As a result, the final polishing (or fine polishing) becomes a crucial step in the process.

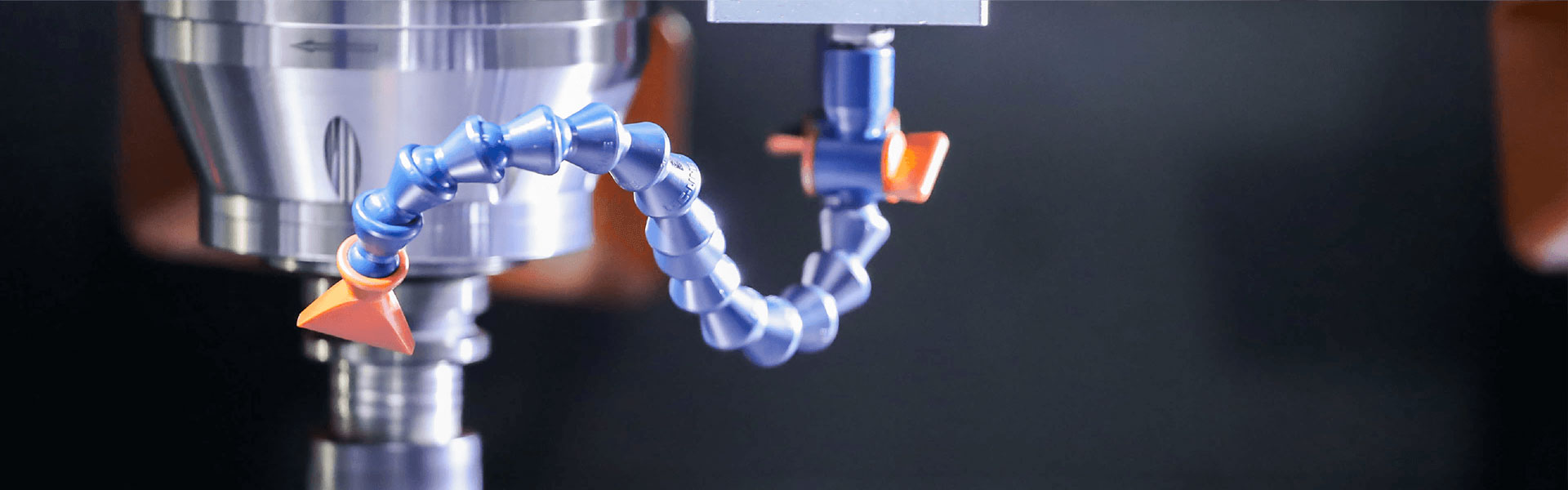

This final polishing typically employs alkaline colloidal silica chemical mechanical polishing (CMP) technology. This method combines the effects of chemical corrosion and mechanical abrasion to efficiently and accurately remove tiny imperfections and impurities from the silicon wafer surface.

However, while traditional CMP technology is effective, the equipment can be expensive, and achieving the required precision for smaller line widths may be challenging with conventional polishing methods. Therefore, the industry is exploring new polishing technologies, such as dry chemical planarization plasma technology (D.C.P. plasma technology), for digitally controlled silicon wafers.

![]()

D.C.P plasma technology is a non-contact processing technology. It uses SF6 (sulfur hexafluoride) plasma to etch the silicon wafer surface. By accurately controlling the plasma etching processing time and silicon wafer scanning speed and other parameters, it can Achieve high-precision flattening of the silicon wafer surface. Compared with traditional CMP technology, D.C.P technology has higher processing accuracy and stability, and can significantly reduce the operating cost of polishing.

During the D.C.P processing process, special attention needs to be paid to the following technical issues:

Control of the plasma source: Ensure that parameters such as SF6 (plasma generation and velocity flow intensity, velocity flow spot diameter (focus of velocity flow)) are accurately controlled to achieve uniform corrosion on the surface of the silicon wafer.

Control accuracy of the scanning system: The scanning system in the X-Y-Z three-dimensional direction of the silicon wafer needs to have extremely high control accuracy to ensure that every point on the surface of the silicon wafer can be processed accurately.

Processing technology research: In-depth research and optimization of the processing technology of D.C.P plasma technology are required to find the best processing parameters and conditions.

Surface damage control: During the D.C.P processing process, the damage on the surface of the silicon wafer needs to be strictly controlled to avoid adverse effects on the subsequent preparation of IC chip circuits.

Although D.C.P plasma technology has many advantages, since it is a new processing technology, it is still in the research and development stage. Therefore, it needs to be treated with caution in practical applications and technical improvements and optimizations continue.

![]()

In general, final polishing is an important part of the silicon wafer processing process, and it is directly related to the quality and performance of the IC chip circuit. With the continuous development of the semiconductor industry, the quality requirements for the surface of silicon wafers will become higher and higher. Therefore, continuous exploration and development of new polishing technologies will be an important research direction in the field of silicon wafer processing in the future.

Semicorex offers high-quality wafers. If you have any inquiries or need additional details, please don't hesitate to get in touch with us.

Contact phone # +86-13567891907

Email: sales@semicorex.com